Instruction pipelining enhances CPU throughput by overlapping the execution of multiple instruction stages, increasing instruction-level parallelism within a single execution unit. Superscalar execution further boosts performance by dispatching multiple instructions simultaneously across several execution units, eliminating pipeline stalls and improving overall processing efficiency. Explore the detailed mechanisms and benefits of both techniques to understand their impact on modern processor architectures.

Main Difference

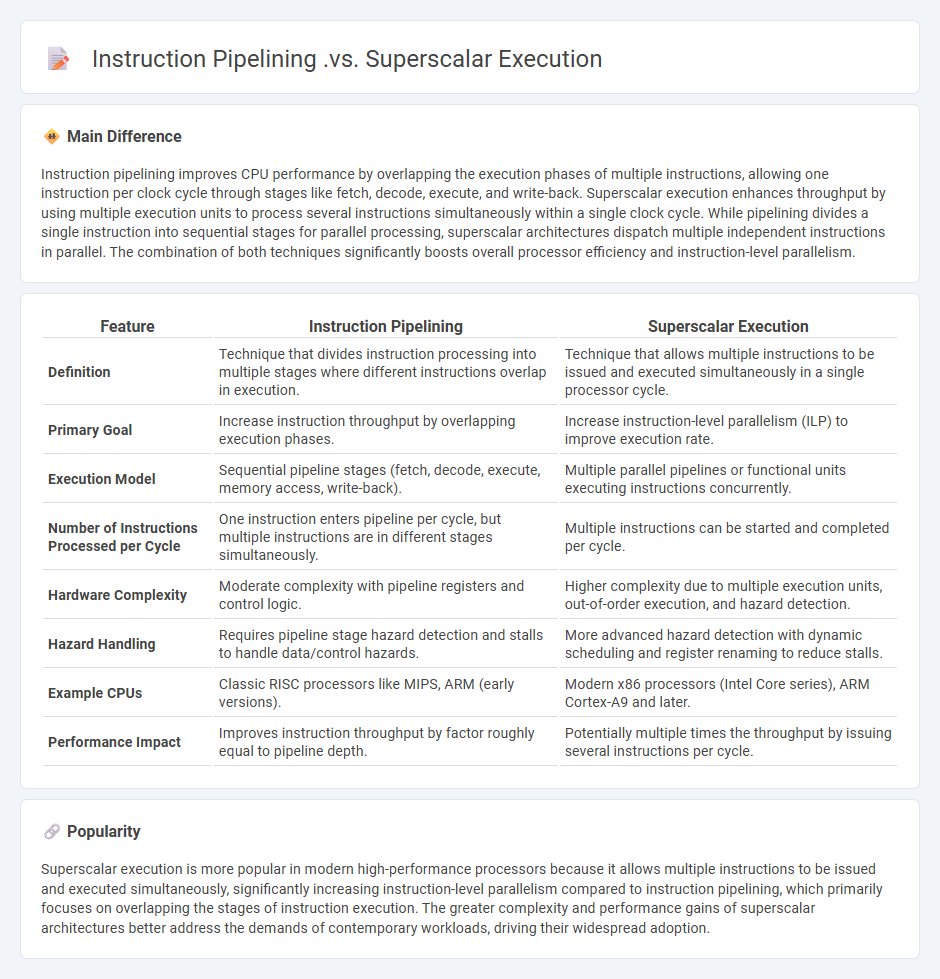

Instruction pipelining improves CPU performance by overlapping the execution phases of multiple instructions, allowing one instruction per clock cycle through stages like fetch, decode, execute, and write-back. Superscalar execution enhances throughput by using multiple execution units to process several instructions simultaneously within a single clock cycle. While pipelining divides a single instruction into sequential stages for parallel processing, superscalar architectures dispatch multiple independent instructions in parallel. The combination of both techniques significantly boosts overall processor efficiency and instruction-level parallelism.

Connection

Instruction pipelining improves CPU throughput by overlapping the execution of multiple instructions in different pipeline stages, while superscalar architecture enhances this approach by allowing multiple instructions to be issued and executed simultaneously within each pipeline stage. Both techniques aim to increase instruction-level parallelism, optimizing the processor's utilization of resources and boosting overall performance. The combination of pipelining and superscalar execution enables modern CPUs to achieve higher instruction throughput and greater execution efficiency.

Comparison Table

| Feature | Instruction Pipelining | Superscalar Execution |

|---|---|---|

| Definition | Technique that divides instruction processing into multiple stages where different instructions overlap in execution. | Technique that allows multiple instructions to be issued and executed simultaneously in a single processor cycle. |

| Primary Goal | Increase instruction throughput by overlapping execution phases. | Increase instruction-level parallelism (ILP) to improve execution rate. |

| Execution Model | Sequential pipeline stages (fetch, decode, execute, memory access, write-back). | Multiple parallel pipelines or functional units executing instructions concurrently. |

| Number of Instructions Processed per Cycle | One instruction enters pipeline per cycle, but multiple instructions are in different stages simultaneously. | Multiple instructions can be started and completed per cycle. |

| Hardware Complexity | Moderate complexity with pipeline registers and control logic. | Higher complexity due to multiple execution units, out-of-order execution, and hazard detection. |

| Hazard Handling | Requires pipeline stage hazard detection and stalls to handle data/control hazards. | More advanced hazard detection with dynamic scheduling and register renaming to reduce stalls. |

| Example CPUs | Classic RISC processors like MIPS, ARM (early versions). | Modern x86 processors (Intel Core series), ARM Cortex-A9 and later. |

| Performance Impact | Improves instruction throughput by factor roughly equal to pipeline depth. | Potentially multiple times the throughput by issuing several instructions per cycle. |

Instruction-Level Parallelism (ILP)

Instruction-Level Parallelism (ILP) refers to the ability of a CPU to execute multiple instructions simultaneously by identifying and exploiting parallelism within a single instruction stream. Modern processors achieve ILP through techniques such as pipelining, superscalar execution, out-of-order execution, and speculative execution, which help improve instruction throughput and overall performance. The effectiveness of ILP is often limited by data dependencies, control hazards, and resource conflicts, requiring sophisticated hardware mechanisms to maximize parallel execution. Contemporary high-performance CPUs, such as Intel's Core and AMD Ryzen processors, incorporate advanced ILP mechanisms to enhance computing efficiency.

Pipeline Stages

Pipeline stages in computer architecture enhance instruction throughput by dividing execution into discrete steps such as instruction fetch, decode, execute, memory access, and write-back. Each stage processes a different instruction simultaneously, increasing processor efficiency and speed. Modern CPUs implement advanced pipeline techniques, including pipeline depth optimization, hazard detection, and branch prediction to minimize stalls and maintain high instruction-level parallelism. Intel's latest Core processors feature pipelines with up to 20 stages, balancing clock speed and instruction throughput for improved performance.

Hazard Handling (Data, Control, Structural)

Hazard handling in computer architecture involves managing data, control, and structural hazards to maintain pipeline efficiency and correctness. Data hazards occur when instructions depend on the results of previous instructions that are not yet available, requiring techniques like forwarding or stalling to resolve. Control hazards arise from branch instructions affecting the instruction fetch sequence, mitigated using branch prediction and pipeline flushing. Structural hazards happen when hardware resources are insufficient for concurrent instruction execution, addressed by resource duplication or instruction scheduling.

Multiple Execution Units

Multiple Execution Units (MEUs) enhance parallel processing in modern computer architectures by allowing simultaneous operations within a single CPU core. These units handle different arithmetic and logic tasks concurrently, improving instruction throughput and reducing latency. High-performance processors from Intel and AMD typically feature several execution units, such as ALUs, FPUs, and load/store units, to optimize workload distribution. Efficient scheduling and pipeline design maximize the utilization of MEUs, boosting overall computational speed and efficiency.

Throughput Optimization

Throughput optimization in computer systems focuses on maximizing the processing capacity to handle the highest volume of data or tasks within a given time frame. Techniques such as parallel processing, efficient resource allocation, and load balancing enhance system throughput by minimizing bottlenecks and reducing latency. Modern CPUs with multi-core architectures and hardware acceleration technologies significantly improve throughput for complex computations and data-intensive applications. Monitoring tools like performance counters and profiling software help identify performance constraints and guide targeted optimizations.

Source and External Links

## Instruction PipeliningInstruction Pipelining - A technique used to improve CPU performance by breaking down the execution of instructions into stages, allowing multiple instructions to be processed simultaneously at different stages.

## Superscalar ExecutionSuperscalar Processors - Execute multiple instructions in parallel by using multiple execution units, allowing more than one instruction to be executed per clock cycle, thereby enhancing instruction-level parallelism.

## Comparison and ContrastPipeline and Superscalar Execution - Both enhance CPU performance but differ in how they achieve parallelism: pipelining handles instructions sequentially through stages, while superscalar execution handles multiple instructions concurrently across different units.

FAQs

What is instruction pipelining?

Instruction pipelining is a CPU technique that divides instruction execution into overlapping stages, increasing instruction throughput and processor efficiency.

What is superscalar execution?

Superscalar execution is a CPU architecture technique that allows multiple instructions to be issued and executed simultaneously in a single clock cycle to improve processing throughput.

How does instruction pipelining work?

Instruction pipelining works by breaking down the execution process into discrete stages--fetch, decode, execute, memory access, and write-back--allowing multiple instructions to overlap in these stages simultaneously, thus increasing CPU throughput and efficiency.

How does superscalar execution improve performance?

Superscalar execution improves performance by enabling a processor to issue multiple instructions per clock cycle, increasing instruction-level parallelism and throughput.

What are the key differences between pipelining and superscalar architecture?

Pipelining divides instruction execution into sequential stages allowing multiple instructions to overlap in processing, while superscalar architecture issues multiple instructions per clock cycle using multiple execution units to achieve parallelism.

What challenges are faced in instruction pipelining?

Instruction pipelining faces challenges such as data hazards, control hazards, structural hazards, pipeline stalls, and branch prediction inaccuracies.

Why is superscalar processing important in modern CPUs?

Superscalar processing enhances modern CPU performance by enabling multiple instructions to execute simultaneously, increasing instruction throughput and improving overall efficiency.

calledges.com

calledges.com