CMOS (Complementary Metal-Oxide-Semiconductor) technology combines both NMOS and PMOS transistors to achieve low power consumption and high noise immunity in integrated circuits. NMOS (N-Channel Metal-Oxide-Semiconductor) transistors are faster due to higher electron mobility but consume more power when switching. Explore the detailed performance comparisons and applications of CMOS and NMOS to better understand their roles in modern electronics.

Main Difference

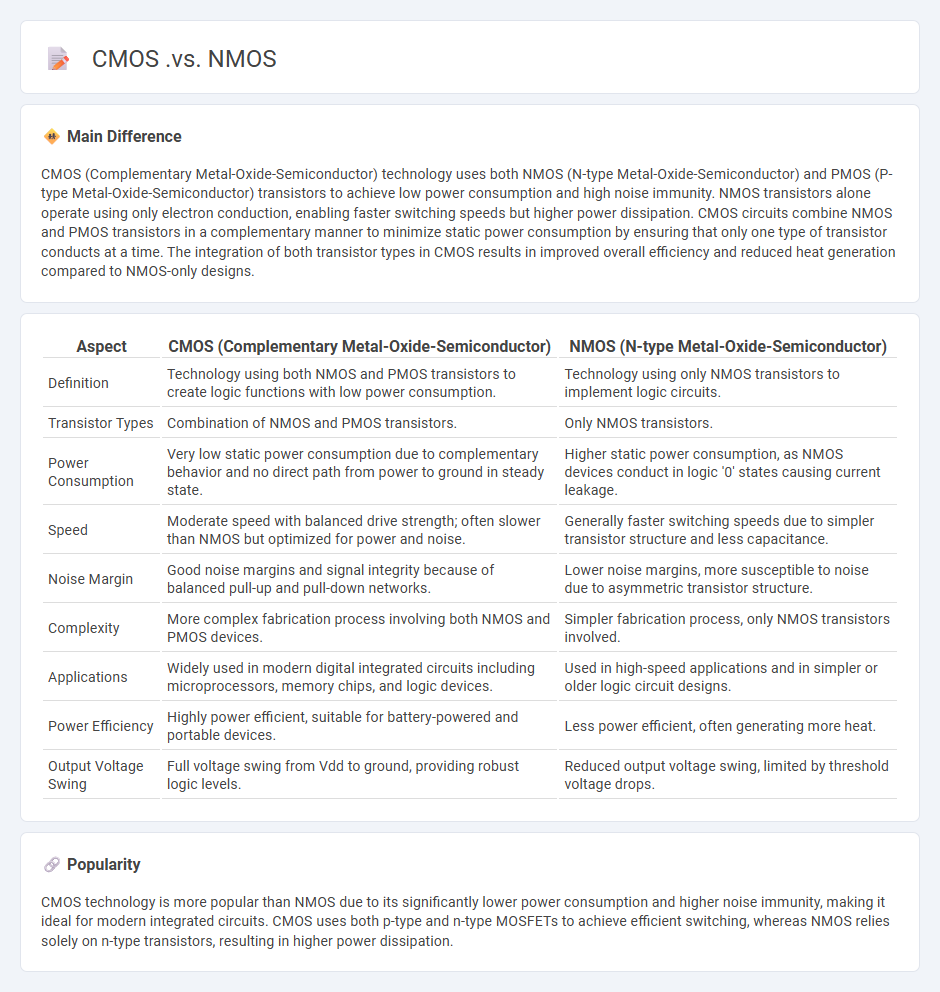

CMOS (Complementary Metal-Oxide-Semiconductor) technology uses both NMOS (N-type Metal-Oxide-Semiconductor) and PMOS (P-type Metal-Oxide-Semiconductor) transistors to achieve low power consumption and high noise immunity. NMOS transistors alone operate using only electron conduction, enabling faster switching speeds but higher power dissipation. CMOS circuits combine NMOS and PMOS transistors in a complementary manner to minimize static power consumption by ensuring that only one type of transistor conducts at a time. The integration of both transistor types in CMOS results in improved overall efficiency and reduced heat generation compared to NMOS-only designs.

Connection

CMOS technology combines complementary NMOS and PMOS transistors in a single integrated circuit to optimize power efficiency and switching speed. In a CMOS inverter, the PMOS transistor connects between the positive supply voltage (VDD) and the output, while the NMOS transistor connects between the output and ground (GND). This complementary configuration allows the circuit to efficiently switch states while minimizing static power consumption.

Comparison Table

| Aspect | CMOS (Complementary Metal-Oxide-Semiconductor) | NMOS (N-type Metal-Oxide-Semiconductor) |

|---|---|---|

| Definition | Technology using both NMOS and PMOS transistors to create logic functions with low power consumption. | Technology using only NMOS transistors to implement logic circuits. |

| Transistor Types | Combination of NMOS and PMOS transistors. | Only NMOS transistors. |

| Power Consumption | Very low static power consumption due to complementary behavior and no direct path from power to ground in steady state. | Higher static power consumption, as NMOS devices conduct in logic '0' states causing current leakage. |

| Speed | Moderate speed with balanced drive strength; often slower than NMOS but optimized for power and noise. | Generally faster switching speeds due to simpler transistor structure and less capacitance. |

| Noise Margin | Good noise margins and signal integrity because of balanced pull-up and pull-down networks. | Lower noise margins, more susceptible to noise due to asymmetric transistor structure. |

| Complexity | More complex fabrication process involving both NMOS and PMOS devices. | Simpler fabrication process, only NMOS transistors involved. |

| Applications | Widely used in modern digital integrated circuits including microprocessors, memory chips, and logic devices. | Used in high-speed applications and in simpler or older logic circuit designs. |

| Power Efficiency | Highly power efficient, suitable for battery-powered and portable devices. | Less power efficient, often generating more heat. |

| Output Voltage Swing | Full voltage swing from Vdd to ground, providing robust logic levels. | Reduced output voltage swing, limited by threshold voltage drops. |

Power Consumption

Power consumption in engineering quantifies the amount of electrical energy used by devices and systems, typically measured in watts (W) or kilowatts (kW). Efficient power management is crucial in fields such as electronics, automotive, and industrial automation to reduce operational costs and environmental impact. Advanced techniques like power factor correction, energy-efficient components, and renewable energy integration optimize overall consumption. Monitoring tools and smart grids facilitate real-time analysis and control, enhancing performance and sustainability.

Switching Speed

Switching speed in engineering refers to the time required for a device, such as a transistor or relay, to change from one state to another, typically measured in nanoseconds or microseconds. High switching speed is critical in applications like digital circuits, telecommunications, and power electronics, where rapid state transitions enable efficient signal processing and power management. Advances in semiconductor materials, such as gallium nitride (GaN) and silicon carbide (SiC), enhance switching speeds by reducing capacitance and switching losses. Optimization of switching speed directly impacts the performance, energy efficiency, and thermal management of modern electronic systems.

Circuit Complexity

Circuit complexity studies the resources required to implement Boolean functions using logic circuits, focusing on parameters like gate count, depth, and fan-in. It plays a crucial role in optimizing digital circuit design, influencing power consumption, speed, and area on integrated circuits. Advanced techniques in circuit complexity analysis help engineers minimize hardware costs and enhance computational efficiency in microprocessors and embedded systems. Research in this field supports the development of scalable, high-performance digital electronics essential for modern engineering applications.

Noise Margins

Noise margins in engineering define the voltage range within which a digital circuit can tolerate noise without misinterpreting logic levels. Typical noise margin values for TTL circuits are around 0.4V for NMH (Noise Margin High) and 0.4V for NML (Noise Margin Low), ensuring reliable switching between logic states. These margins are critical in designing robust digital systems, as they prevent false triggering caused by signal degradation or electromagnetic interference. Standards such as IEEE 181 facilitate consistent noise margin specifications for complex integrated circuits.

Applications

Engineering applications harness advanced technologies like artificial intelligence, machine learning, and automation to optimize design, manufacturing, and maintenance processes. Civil engineering employs geographic information systems (GIS) and building information modeling (BIM) for infrastructure planning and construction management, enhancing accuracy and efficiency. Mechanical engineering integrates robotics and computational fluid dynamics (CFD) for precision manufacturing and performance analysis of machinery. Electrical engineering utilizes embedded systems and Internet of Things (IoT) devices to develop smart grids and improve energy management solutions.

Source and External Links

CMOS vs NMOS: Which is Better? - Blog - CMOS technology, combining both NMOS and PMOS transistors, offers significantly lower static power consumption and higher power efficiency compared to NMOS, making CMOS the preferred choice in modern integrated circuits.

Difference between CMOS and NMOS Technology - CMOS technology uses complementary NMOS and PMOS devices, resulting in lower power dissipation, higher noise immunity, reduced complexity, and less heat generation than NMOS technology, which only uses N-type transistors.

Difference between CMOS and NMOS Technology - CMOS circuits provide faster switching speeds, lower power supply requirements, higher noise immunity, and lower power dissipation than NMOS circuits, though NMOS offers higher packing density.

FAQs

What is CMOS technology?

CMOS technology, or Complementary Metal-Oxide-Semiconductor technology, is a semiconductor manufacturing process used to create integrated circuits, featuring low power consumption and high noise immunity by combining p-type and n-type MOSFETs.

What is NMOS technology?

NMOS technology uses n-type metal-oxide-semiconductor field-effect transistors (MOSFETs) where electrons serve as charge carriers, offering faster switching speeds and lower power consumption compared to PMOS technology.

What are the main differences between CMOS and NMOS?

CMOS uses both p-type and n-type MOSFETs for low power consumption and high noise immunity, while NMOS uses only n-type MOSFETs resulting in faster switching but higher power consumption; CMOS circuits offer better energy efficiency and less heat dissipation compared to NMOS technology.

How does CMOS improve power efficiency compared to NMOS?

CMOS improves power efficiency by using complementary pairs of p-type and n-type MOSFETs, which minimize static power consumption by ensuring that only one transistor type conducts at a time, significantly reducing leakage current compared to NMOS technology that relies on continuous current flow through a single transistor type.

What are the advantages of using CMOS over NMOS?

CMOS technology offers lower static power consumption, higher noise immunity, better scaling for high-density integration, and reduced heat generation compared to NMOS.

What are the limitations of NMOS circuits?

NMOS circuits have limitations including higher power consumption due to static current flow, slower switching speeds compared to CMOS technology, lack of full voltage swing output leading to reduced noise margins, and increased susceptibility to noise and voltage drops.

Where are CMOS and NMOS commonly used in electronics?

CMOS is commonly used in microprocessors, microcontrollers, and memory chips for low power consumption and high noise immunity, while NMOS is widely utilized in digital logic circuits and high-speed switching applications due to its faster electron mobility.

calledges.com

calledges.com