FinFET technology offers superior control over short-channel effects and reduces leakage current compared to traditional planar MOSFETs, enhancing overall device performance and energy efficiency. The three-dimensional structure of FinFETs allows for higher transistor density and improved scalability in advanced semiconductor nodes. Explore in-depth comparisons and insights to understand which transistor architecture best suits your applications.

Main Difference

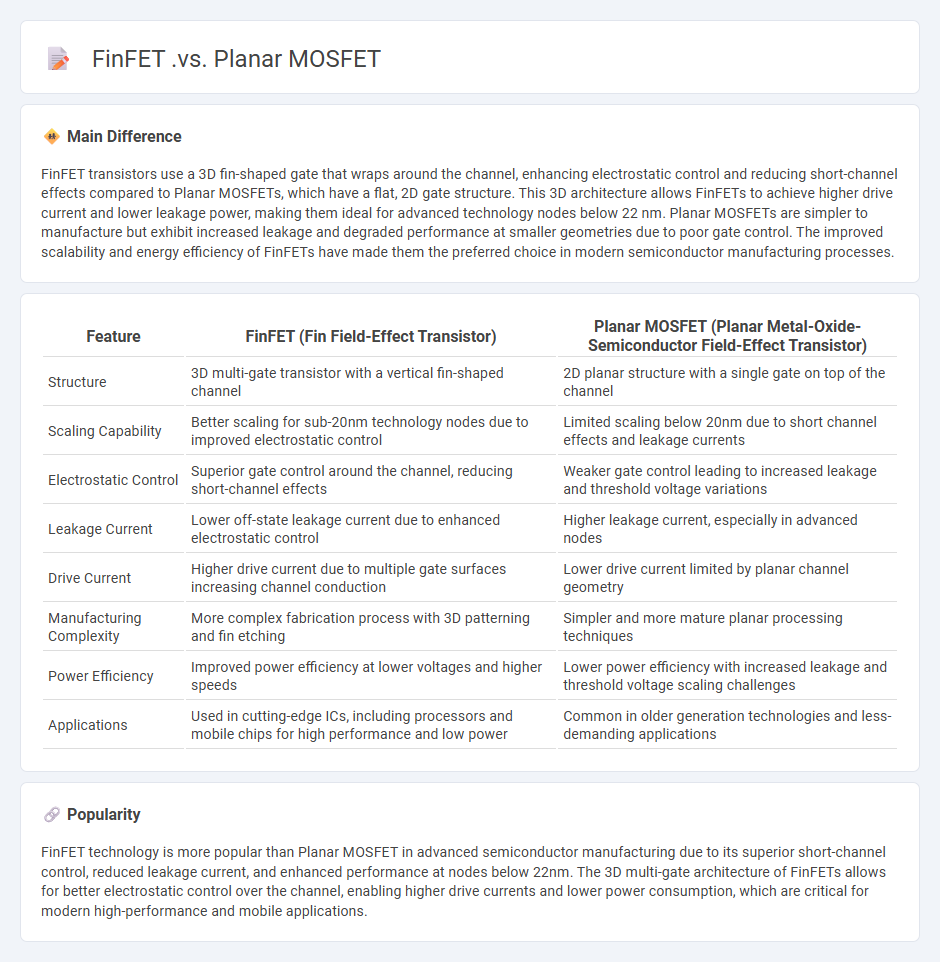

FinFET transistors use a 3D fin-shaped gate that wraps around the channel, enhancing electrostatic control and reducing short-channel effects compared to Planar MOSFETs, which have a flat, 2D gate structure. This 3D architecture allows FinFETs to achieve higher drive current and lower leakage power, making them ideal for advanced technology nodes below 22 nm. Planar MOSFETs are simpler to manufacture but exhibit increased leakage and degraded performance at smaller geometries due to poor gate control. The improved scalability and energy efficiency of FinFETs have made them the preferred choice in modern semiconductor manufacturing processes.

Connection

FinFET and planar MOSFET are connected through their role as fundamental transistor architectures in semiconductor technology, where planar MOSFETs represent traditional flat-channel devices and FinFETs provide a 3D multi-gate structure enhancing control over short-channel effects. The transition from planar MOSFET to FinFET architecture is driven by scaling challenges below 22nm node technologies, enabling improved performance, reduced leakage current, and higher drive current in advanced integrated circuits. Both transistor types are integrated within complementary metal-oxide-semiconductor (CMOS) processes to enable optimized power, speed, and area trade-offs in modern microprocessors and memory devices.

Comparison Table

| Feature | FinFET (Fin Field-Effect Transistor) | Planar MOSFET (Planar Metal-Oxide-Semiconductor Field-Effect Transistor) |

|---|---|---|

| Structure | 3D multi-gate transistor with a vertical fin-shaped channel | 2D planar structure with a single gate on top of the channel |

| Scaling Capability | Better scaling for sub-20nm technology nodes due to improved electrostatic control | Limited scaling below 20nm due to short channel effects and leakage currents |

| Electrostatic Control | Superior gate control around the channel, reducing short-channel effects | Weaker gate control leading to increased leakage and threshold voltage variations |

| Leakage Current | Lower off-state leakage current due to enhanced electrostatic control | Higher leakage current, especially in advanced nodes |

| Drive Current | Higher drive current due to multiple gate surfaces increasing channel conduction | Lower drive current limited by planar channel geometry |

| Manufacturing Complexity | More complex fabrication process with 3D patterning and fin etching | Simpler and more mature planar processing techniques |

| Power Efficiency | Improved power efficiency at lower voltages and higher speeds | Lower power efficiency with increased leakage and threshold voltage scaling challenges |

| Applications | Used in cutting-edge ICs, including processors and mobile chips for high performance and low power | Common in older generation technologies and less-demanding applications |

Gate Control

Gate control in engineering refers to mechanisms that regulate the flow of electrical signals or fluids within a system. In semiconductor devices, gate control modulates current by varying voltage at the gate terminal, as seen in MOSFETs, optimizing switching speed and power efficiency. In fluid dynamics, gate systems manage water flow in dams or channels, ensuring precise control over discharge rates to prevent flooding and maintain system stability. Advanced gate control technologies integrate sensors and automation for real-time adjustments, enhancing overall operational performance.

Short-Channel Effects

Short-channel effects (SCE) significantly impact the performance and reliability of MOSFETs as device dimensions shrink below 100 nm. These effects include threshold voltage roll-off, drain-induced barrier lowering (DIBL), and velocity saturation, which degrade transistor switching characteristics and increase leakage currents. Advanced engineering techniques such as strained silicon channels, high-k dielectrics, and multi-gate structures are employed to mitigate SCE in modern integrated circuits. Understanding and controlling short-channel effects is critical for the continued scaling of semiconductor devices in the microelectronics industry.

Leakage Current

Leakage current in engineering refers to the unwanted flow of electrical current through an insulating material or device when it is supposed to be non-conductive. This phenomenon commonly occurs in capacitors, semiconductors, and electrical insulation, resulting in energy loss, heating, or degradation of components. Leakage currents are typically measured in microamperes (uA) or nanoamperes (nA) and are critical factors in designing reliable electrical systems and circuits. Minimizing leakage current improves device efficiency, safety, and longevity, especially in power electronics and high-voltage applications.

Channel Mobility

Channel mobility in engineering refers to the dynamic allocation and reconfiguration of communication channels within network systems to enhance data transmission efficiency. This concept is crucial in mobile ad hoc networks (MANETs), allowing devices to switch frequencies or routes to maintain connectivity and reduce interference. Techniques such as cognitive radio and software-defined networking (SDN) leverage channel mobility to optimize spectrum utilization and adapt to changing network conditions. Effective implementation of channel mobility improves system robustness, latency, and overall network throughput in wireless communications.

Scaling Limitations

Scaling limitations in engineering frequently result from physical constraints, such as material strength and thermal management, which hinder the proportional increase of system size or capacity. Computational systems face bottlenecks like memory bandwidth and processor speed that restrict performance scaling despite advancements in hardware. Manufacturing precision and cost scaling also impose practical limits when scaling complex structures or devices. Addressing these challenges requires innovative approaches in materials science, system architecture, and process optimization to achieve sustainable growth.

Source and External Links

Finfet vs Mosfet: What are Differences - Avaq Semiconductor - FinFETs have a three-dimensional fin structure offering superior subthreshold slope, lower leakage current, better power efficiency, faster switching speed, and better scalability compared to traditional planar MOSFETs which have simpler planar structures but higher leakage and limited scalability.

Using FinFETs vs. MOSFETs for IC Design | System Analysis Blog - FinFETs are 3D transistors with vertical fins wrapped by the gate providing better electrostatic control and short-channel behavior than planar MOSFETs, enabling higher scalability and integration in modern IC designs.

Difference Between FinFET and MOSFET - Nantian Electronics - FinFET technology, with its fin-shaped channel surrounded by a gate structure, significantly reduces leakage current and power dissipation while offering enhanced scalability and performance over traditional planar MOSFETs.

FAQs

What is a MOSFET?

A MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) is a semiconductor device used to amplify or switch electronic signals in circuits.

What are the differences between FinFET and Planar MOSFET?

FinFET uses a 3D fin-shaped channel to improve gate control and reduce short-channel effects, whereas Planar MOSFET has a flat 2D channel. FinFET offers lower leakage current, higher drive current, better scalability below 20nm technology nodes, and improved subthreshold slope compared to Planar MOSFET.

How does a FinFET work?

A FinFET works by using a thin silicon fin as the transistor channel, surrounded by a gate electrode on three sides to improve control over the channel, reducing leakage current and enabling better performance at smaller nodes.

What are the key advantages of FinFET over Planar MOSFET?

FinFET offers superior short-channel control, reduced leakage current, higher drive current, improved scalability below 20 nm, and enhanced energy efficiency compared to Planar MOSFET.

What are the design challenges of FinFET technology?

FinFET technology design challenges include controlling short-channel effects, managing variability in fin dimensions, ensuring accurate doping profiles, optimizing fin height and width for performance, addressing increased layout complexity, and mitigating parasitic capacitances and resistances to improve overall device reliability and scalability.

How do FinFETs improve device performance?

FinFETs improve device performance by enhancing gate control over the channel, reducing short-channel effects, lowering leakage current, and enabling higher drive current for faster switching speeds.

Why are FinFETs used in modern processors?

FinFETs are used in modern processors because they provide reduced leakage current, improved control over short-channel effects, higher switching speed, and lower power consumption compared to traditional planar transistors.

calledges.com

calledges.com